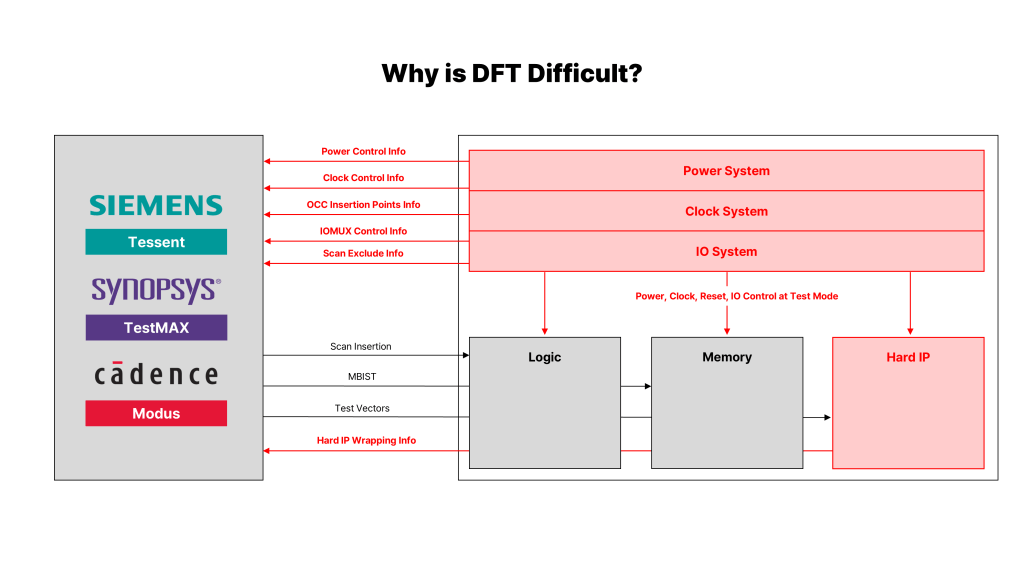

As we looked at in the last column, the concept of DFT is not that difficult. However, as chips have become more complex, the simple and straightforward DFT has now become an advanced specialized field.

Let’s take SCAN, which tests flip-flops, as an example.

In the late 1990s, the number of flip-flops was only several hundred thousand, but since the 2020s, it has increased to tens of millions or even hundreds of billions. This means that the data to be tested has increased, and accordingly, the testing time and cost have increased. Accordingly, technologies to improve test efficiency have been developed, and one of them is SCAN compression. It is a technology that compresses data to reduce the test time and vector size, i.e. test data. However, since data must not be lost while compressing, and must be accurately reproduced to the state before compression when decompressing, a very sophisticated algorithm is required. The current complexity makes it almost impossible for designers to do it by hand, but fortunately, the tool automatically performs it.

There is already a commercial tool for Scan.

The problem is that even with the tool, DFT configuration is not good.

Why is DFT configuration not good when there is a tool?

Let’s take a closer look at the situation for configuring SCAN. As mentioned in the Clock Canvas story, a separate Test clock is required to run SCAN. And a Flip-flop is required to configure this Test Clock circuit within the Clock System. So, can this Flip-flop perform SCAN? Or not? If SCAN is performed, how far should SCAN be performed, and who will make and provide the clock that drives SCAN?

The same goes for the Power System. If you tie the Power System to SCAN, you cannot operate SCAN. Because SCAN operates only when power is supplied to the circuit, if the flip-flop responsible for RESET or power gating of the Power System is connected to SCAN and operated, the flip-flop may be turned off or forcibly changed to reset depending on the test data. This causes a system error when the power is turned off or the system is reset during the test. Then, does the Power System not need to perform SCAN? If there is a problem with the Power System, the chip will not operate at all, so the Power System should perform SCAN as much as possible.

If we organize the problems in SCAN, they occur when the system to be tested and the SCAN (test) system are intertwined. They mainly occur in the infrastructure system that is basically required to operate the test circuit, and it is necessary to redefine the infrastructure systems that are intertwined with the DFT system configuration. Power, clock system, and IO system are included here.

I have only mentioned SCAN as an example, but the same goes for BIST for memory testing and hard IP test systems.

In the end, in order to properly configure DFT in SOC, the following three infrastructures need to be redefined.

1. Power System that turns the test circuit on and off

2. Clock System that operates the test circuit

3. I/O System that sends and receives the data to be tested

지난 컬럼에서 살펴 본 것처럼 DFT의 개념은 크게 어렵지가 않습니다. 하지만, 칩이 복잡해지면서, 간단하고 심플했던 DFT가 이제는 고도화된 전문 영역이 되었습니다.

Flip-flop을 테스트하는 SCAN을 예로 들어 보겠습니다.

1990년대 후반만 하더라도 Flip-flop의 수가 수십만개에 불과했는데, 2020년대 이후에는 수천만개에서 많게는 수백억개 이상이 되었습니다. 이 얘기는 테스트 해야 할 데이터가 그만큼 많아졌다는 얘기이고, 그에 따라 테스트 시간과 비용이 증가하게 되었다는 얘기죠. 이에 따라서 테스트 효율화 기술들이 개발되었고 그중 하나가 SCAN compression 입니다. 데이터를 압축해서 테스트 시간과 벡터 즉, 테스트 데이터의 크기를 줄이는 기술입니다. 그런데 compression을 하면서도 데이터가 빠지지 않도록 해야 하고, 복원 (decompression)을 할 때도 압축하기 이전 상태로 정확하게 재현해야 하기 때문에 굉장히 정교한 알고리즘이 필요하게 됩니다. 지금의 복잡도는 설계자가 손으로 하는 것은 거의 불가능한데, 다행히도 Tool에서 자동으로 진행해줍니다.

Scan은 이미 상용화 Tool이 있습니다.

문제는 Tool이 있어도 DFT 구성이 잘 안된다는 것입니다.

Tool이 있는데 DFT 구성은 왜 잘 안되는 걸까요?

SCAN을 구성하기 위한 상황을 조금 더 살펴보겠습니다.

Clock Canvas 이야기에서 말한 것처럼 SCAN을 돌리려면 별도의 Test clock이 필요합니다. 그리고 Clock System내에 이러한 Test Clock 회로를 구성하려면 Flip-flop이 필요합니다. 그렇다면 이 Flip-flop은 SCAN을 할 수 있을까요? 없을까요? SCAN을 한다면 어디까지 SCAN을 해야 하며, SCAN을 구동하는 clock은 누가 만들어서 줄까요?

Power System도 마찬가지 입니다. Power System을 SCAN에 엮어 버리면, SCAN을 동작 시킬 수 없습니다. 왜냐하면 SCAN은 회로에 Power가 들어온 상태에서만 동작하는데, Power System의 RESET이나 Power Gating을 담당하는 Flip-flop을 SCAN에 엮어서 동작 시키면, Test 데이터에 따라 해당 Flip-flop이 꺼지거나 reset 상태로 강제로 바뀔 수 있기 때문입니다. 이로 인해 테스트하다가 Power가 꺼지거나 시스템이 리셋 되면서 시스템 오류가 발생하게 되죠. 그럼 Power System은 SCAN을 안 해도 될까요? Power System에 문제가 발생하면, 칩이 전혀 동작하지 않기 때문에, Power System은 최대한 SCAN을 진행해야 합니다.

SCAN에서의 문제를 정리해보면, 테스트의 대상이 되는 시스템과 SCAN(테스트) 시스템이 서로 얽혀 있을 때 발생합니다. 주로 테스트 회로를 동작 시키는데 기본적으로 있어야 하는 인프라 시스템에서 발생하고 있는데요, DFT시스템 구성과 얽히는 인프라 시스템들을 다시 한번 정의할 필요가 있습니다. Power와 Clock system, IO sytem이 여기에 해당이 됩니다.

SCAN만 예로 들어 얘기했지만, Memory 테스트를 위한 BIST나, Hard IP 테스트 시스템도 마찬가지입니다.

결국 SOC에서 DFT를 잘 구성하려면, 아래 3개의 인프라에 대한 재정의가 필요합니다.

1. Test 회로를 끄고 켜는 Power System

2. Test 회로를 동작 시키는 Clock System

3. Test할 Data를 잘 주고 받는 I/O System