The clock has a simple waveform, but it is not a simple signal. This is because everything inside the SOC chip moves based on this clock.

The process performs calculations, data moves on the bus, and everything reads and writes from memory moves based on the clock. The clock is the reference of the system.

The reference of the system means that there must be no error at all. If the reference is shaken, the entire system will shake. The more complex the system, the more the small instability of the reference will have a big impact, so the stability of the clock becomes more important in complex SOCs.

A clock that toggles between 0 and 1 is considered to be one cycle from 0 to 1 and back to 0. A CPU of 3GHz means that this cycle repeats 3 billion times per second. Not only are the waveforms that toggle between 0 and 1 3 billion times per second used by billions of transistors in the CPU, but they are also connected to different clock domains such as memory and I/O. But what if there is an error in this clock?

If the clock is late, the data does not arrive on time, and the calculation results are tangled, and if the clock is fast, the next calculation is executed before the data arrives.

If the clock is irregular, the system will not know when to do what, and this can cause the system to stop.

The situation is no different even at a low frequency of 48kHz. The errors that occur when the clock is slow, fast, or unstable are the same. However, since it is 48,000 toggles per second, it can be said that it is a little more than 3 billion times.

For these reasons, most companies that already have a clock system in some form try not to touch the clock system. If you touch it incorrectly, it will not only affect normal operation, but in the worst case, the chip will not work.

If you compare the clock to a heartbeat, what would happen if a person tried to artificially control the heartbeat? Most people would die.

The chip would just stop, but if the clock stops, the chip stops. If the chip stops, most fabless companies would stop their business.

Therefore, they try to maintain the existing system that was working well, and they try not to change it unless absolutely necessary. Even companies with a very long history tend to utilize legacy designs. The clock system is an area that is very conservative about changes. Given this situation, there are only a very small number of people in the world who have actually designed clock components.

However, since it is the reference of the system, the clock basically has to continuously generate waveforms like a heartbeat that has to keep beating without stopping if it is alive. Therefore, it continuously consumes power. You can consider it to consume more than 30~50% of the total system power.

So, as I mentioned in the “Asynchronous design is the basic” section, power consumption is reduced by using multiple clocks such as 3GHz and 1GHz, but this alone is not enough.

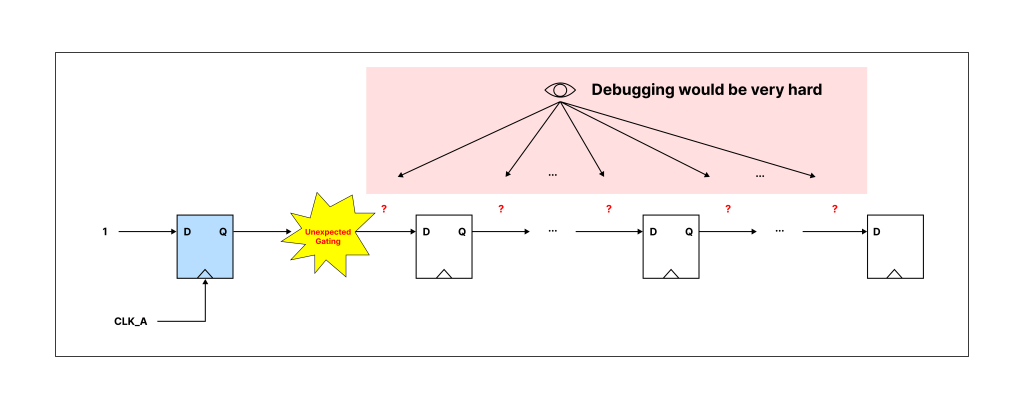

Like Power Gating in the previous Power Canvas column, clock gating, a technology that cuts off the power supply when the clock is not in use, is mostly used in complex SOC chips. However, as shown in the figure above, if CLK_A is gated at an unwanted moment and the value 1 is not properly updated in the next cycle, unexpected behavior can occur in the latter part. The problem is that it is impossible to know when and where such errors will occur. Since they can occur only under certain conditions or only in certain input patterns, errors that are not easily reproduced by simple tests occur very randomly and are difficult to debug.

The more complex the chip, the more power it consumes. As higher frequencies are used for higher performance, the power consumption ratio of the clock, which is the reference of the system, increases. Therefore, the higher the performance and function of the chip, the more stable the clock must be provided, and more care must be taken to control it so that it consumes less power. Ultimately, as the complexity of the chip increases, the complexity of the clock increases exponentially, and the clock system design becomes more difficult.

clock은, 파형은 단순하지만, 단순한 신호가 아닙니다. SOC 칩 안에서 모든 것이 이 clock을 기준으로 움직이기 때문이죠.

프로세스가 연산을 수행하고, 데이터가 버스를 타고 이동하고, 메모리에서 읽고 쓰는 모든 것이 clock을 기준으로 맞춰서 움직이게 됩니다. clock은 시스템의 레퍼런스입니다.

시스템의 레퍼런스가 된다는 것은, 한 치의 오차도 없어야 한다는 얘기입니다. 레퍼런스가 흔들리면, 시스템 전체가 흔들리기 때문입니다. 시스템이 복잡하면 복잡할 수록 레퍼런스의 작은 불안정도 크게 영향을 미치게 되기 때문에 복잡한 SOC일수록 clock의 안정성은 더욱 중요해지게 됩니다.

0과 1을 토글하는 clock은 0에서 1이 되었다 다시 0으로 떨어지는 것을 한 주기로 봅니다. CPU 3GHz라는 것은 이 주기가 초당 30억번을 반복 한다는 뜻입니다. 초당 30억번의 0과 1을 토글을 하는 파형을 CPU 안에 있는 수십억개의 트랜지스터들이 사용할 뿐 아니라, 메모리와 I/O 같은 서로 다른 clock 도메인으로도 연결이 되는 것입니다. 그런데 이 clock에 오차가 생긴다?

clock이 늦어지면 데이터가 제시간에 도착하지 못하고, 연산 결과는 꼬이게되고

clock이 빨라지면 데이터가 도착하기도 전에 다음 연산이 실행되어버립니다.

clock이 불규칙하면 시스템은 언제 뭘 해야 하는지 알 수 없게 되고, 이로 인해 시스템이 멈춰버릴 수도 있습니다.

48kHz의 낮은 주파수라고 해서 사정이 다르지는 않습니다. clock이 늦어지거나 빨라지거나 불안정할 때 발생하는 오류는 동일합니다. 다만, 초당 48,000번의 토글이다 보니 30억번의 보다는 조금 여유가 있는 정도라고 할 수 있겠네요

이런 이유들로 이미 어떤 형태로든 Clock 시스템을 가지고 있는 대부분의 회사에서는 Clock 시스템을 손대지 않으려고 합니다.

잘못 손대면 정상 동작에도 영향을 줄 뿐아니라, 최악의 경우 칩이 동작하지 않기 때문이죠.

클럭을 심장 박동에 비유했는데, 사람이 심장 박동을 인위적으로 조절하려고 하면 어떻게 될까요? 대부분 죽을 겁니다.

칩은 그냥 멈추는 수준에서 끝나긴 하겠지만, 클럭이 멈추면 칩이 멈춥니다. 칩이 멈추면 대부분의 팹리스는 비즈니스가 멈추겠죠.

따라서 기존에 잘 돌던 시스템을 유지하려고 하지, 웬만해선 변경하려고 하지 않습니다. 업력이 매우 오래된 회사들도, legacy 디자인을 활용하는 경향이 매우 큽니다. Clock 시스템은 변경에 매우 보수적인 영역입니다.

상황이 이렇다 보니, Clock component를 실제로 디자인해 본 사람은 전세계를 통 털어서 매우 소수일 수 밖에 없습니다.

하지만, 시스템의 레퍼런스다 보니 clock은 기본적으로 살아 있다면, 쉬지 않고 뛰어야 하는 심장 박동처럼 계속 파형을 만들어내야 합니다. 따라서 계속 power를 소모하고 있습니다. 전체 시스템 파워의 30~50%이상은 소모한다고 보시면 됩니다. 그래서 “Asynchronous 설계가 기본임” 편에서 얘기한 것처럼 3GHz, 1GHz등을 여러 개의 clock을 써서 power 소모를 줄이기도 하는데, 이것만으로는 부족합니다.

이전의 Power Canvas 컬럼에서의 Power Gating 처럼, clock도 사용하지 않을 때는 전원 공급을 끊는 기술, 즉 Clock Gating을 복잡한 SOC 칩에서는 대부분 사용합니다.

하지만, 아래 그림에서 처럼 CLK_A가 원치 않는 순간에 gating이 되어서 1이라는 값이 다음 사이클에 적절하게 업데이트 되지 않았을 때, 뒷 부분에서 예상치 못한 동작이 발생할 수 있습니다. 문제는 이러한 오류가 언제 어디서 발생할지 알 수가 없다는 것입니다. 특정 조건에서만 발생하거나 특정 입력 패턴에서만 문제가 드러날 수도 있기 때문에, 단순한 테스트만으로는 쉽게 재현 되지 않는 오류가 굉장히 랜덤하게, 디버깅하기 어려운 현상이 발생하게 되는 것이죠.

복잡한 칩일수록 power소모는 클 수 밖에 없습니다. 더 높은 성능을 위해 더 높은 주파수를 사용하다 보니 시스템의 레퍼런스인 clock의 power 소모 비율은 더 커집니다. 따라서 고성능, 고기능 칩일수록 clock을 더 안정적으로 제공해야 하고, 더 적은 power를 소모하도록 제어하기 위해 더 많은 신경을 써줘야 합니다. 결국 칩의 복잡도가 증가할 수록, clock 의 복잡도는 기하급수적으로 증가하게 되고, 그만큼 clock 시스템 설계가 어려워집니다.